تماس با ما

تماس بگیرید: 03532330313

03532347513-16

سبد خرید

هیچ محصولی وجود ندارد

تعیین خواهد شد ارسال

0 ریال مجموع

محصول با موفقیت به سبد خرید اضافه شد

تعداد

مجموع

0 محصول در سبدخرید شما وجود دارد. یک محصول در سبدخرید شما وجود دارد.

جمع محصولات

جمع هزینه حمل تعیین خواهد شد

مجموع (بدون ماليات)

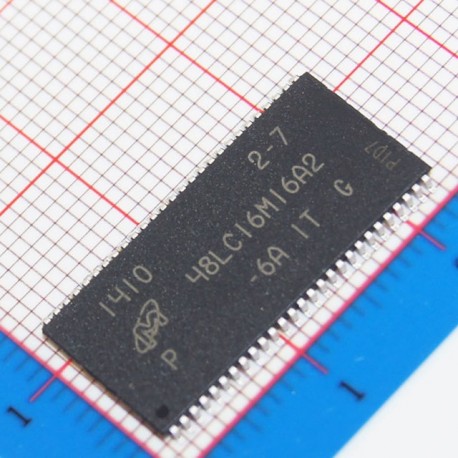

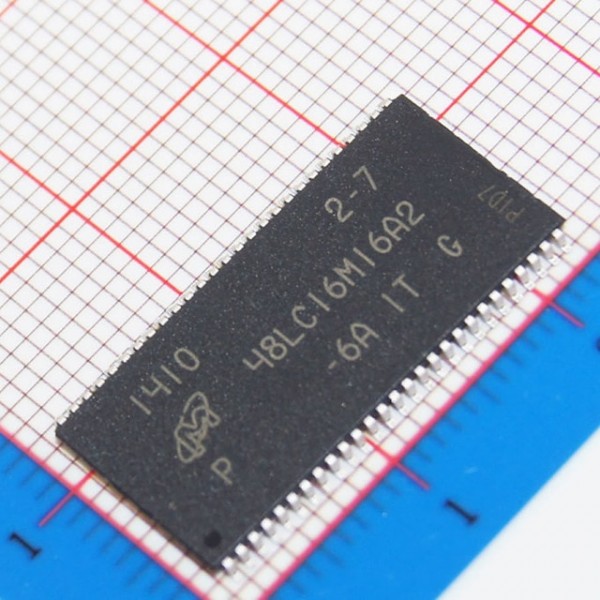

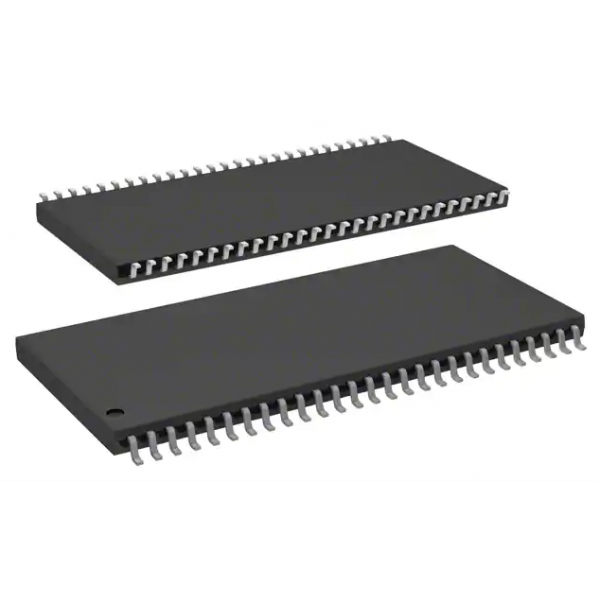

رم MT48LC16M16A2P-6AIT TSOP54 SDR SDRAM- new&original

با خرید این محصول 3 امتیاز وفاداری. سبد شما در مجموع 3 امتیاز وفاداری که می تواند به کوپن تخفیف تبدیل شود به ارزش 15,000 ریال.

نظر و رتبه بندی مشتریان

4022000

محصول جدید

3,894,000 ریال

رم MT48LC16M16A2P - کاملا نو و اورجینال

The MT48LC16M16A2P-6A IT is a 256Mb SDR SDRAM uses an internal pipelined architecture to achieve high-speed operation. This architecture is compatible with the 2n rule of prefetch architectures, but it also allows the column address to be changed on every clock cycle to achieve a high-speed, fully random access. Precharging one bank while accessing one of the other three banks will hide the precharge cycles and provide seamless, high-speed and random-access operation. This is a high-speed CMOS, dynamic random-access memory containing 268435456-bits. It is internally configured as a quad-bank DRAM with a synchronous interface. Read and write accesses to the SDRAM is burst-oriented, accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an active command, which is then followed by a read or write command.

- PC100 and PC133-compliant

- Fully synchronous, all signals registered on positive edge of system clock

- Internal banks for hiding row access/precharge

- Auto precharge, includes concurrent auto precharge and auto refresh modes

- Self refresh mode

- LVTTL-compatible inputs and outputs